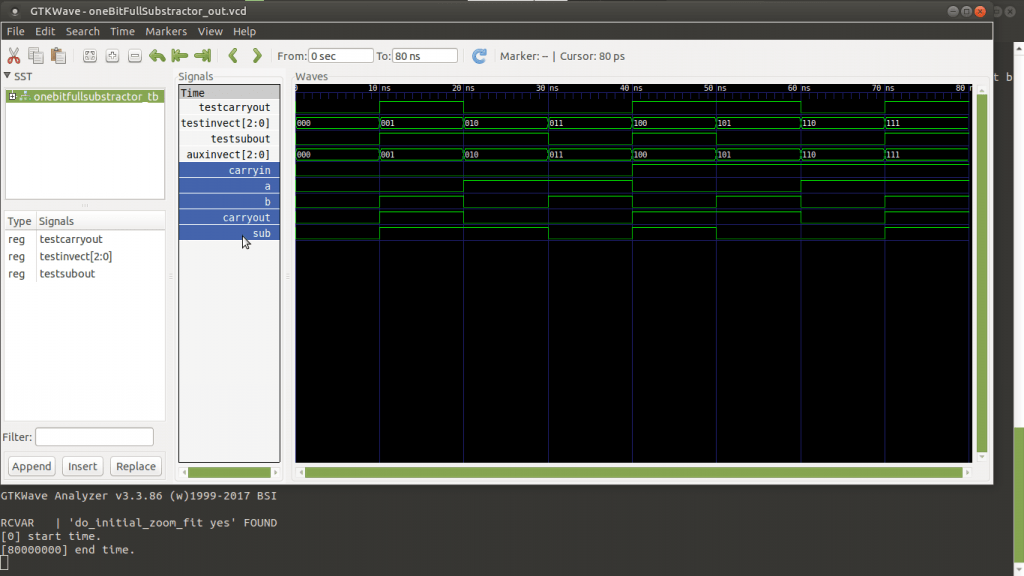

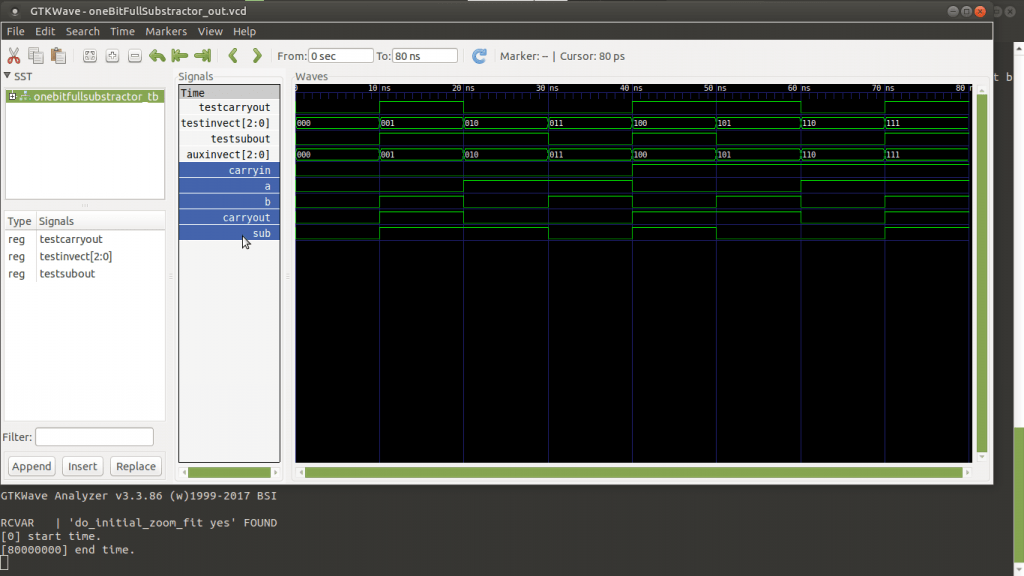

Aquí dejo otro code-kata en VHDL, ahora para construir un restador completo de 1 bit. Recibe 3 entradas y saca 2 salidas. Es muy parecido al sumador completo del post anterior.

Continuar leyendo..

Aquí dejo otro code-kata en VHDL, ahora para construir un restador completo de 1 bit. Recibe 3 entradas y saca 2 salidas. Es muy parecido al sumador completo del post anterior.

Continuar leyendo..

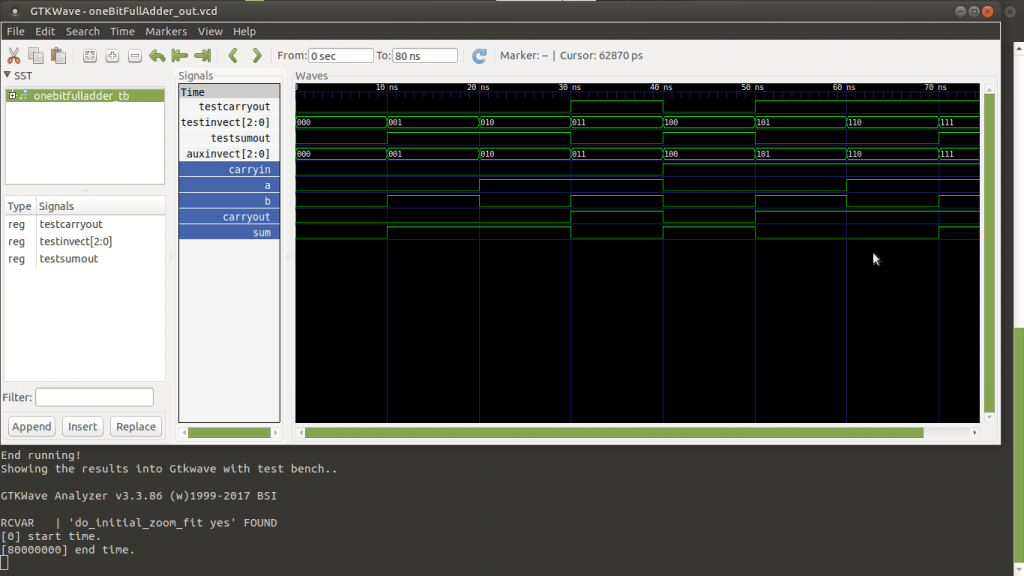

Traigo un code-kata de un circuito digital. Se trata de un sumador completo de 1 bit. Es decir, es un circuito con 3 entradas y 2 salidas. Las tres entradas son: un acarreo, y los dos bits que vamos a sumar.

Continuar leyendo..