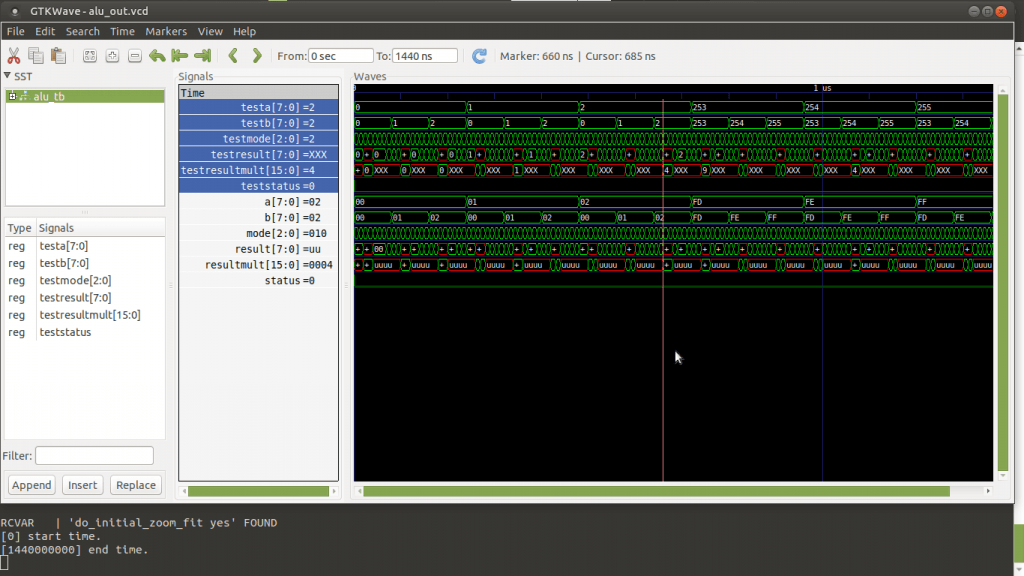

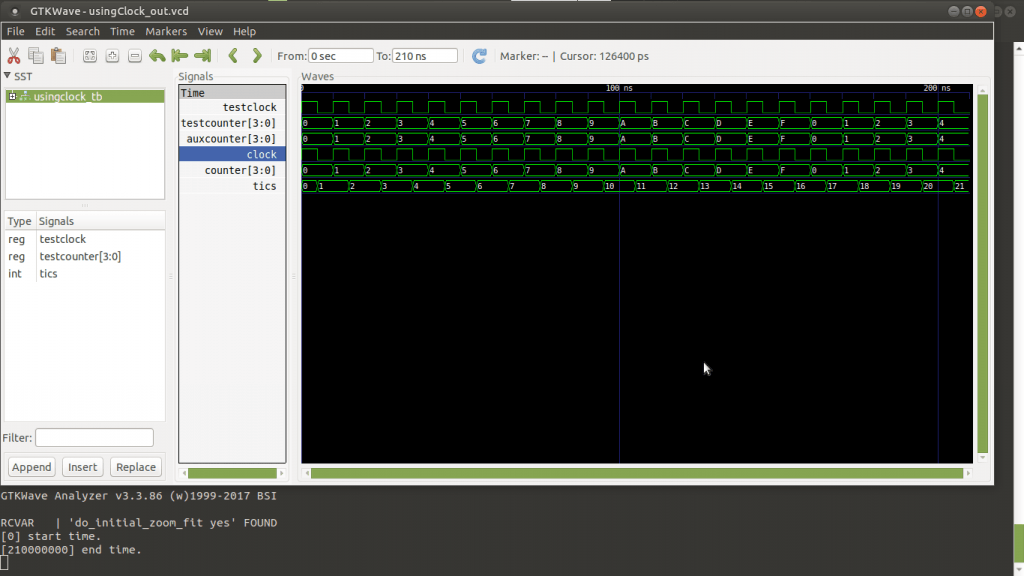

Sigo diseñando sencillos circuitos digitales en VHDL. Así que aquí estoy de nuevo con otro code-kata, ahora simulando en el banco de pruebas, el tic tac de un reloj interno que muchos circuitos electrónicos tienen dentro. Es decir, muchas veces tendremos que desencadenar acciones en circuitos al son del tic tac de un reloj o varios. Para simular este tic tac que tendremos que generar estas señales 10101010101.. cambiando de 0 a 1, y de 1 a 0, cada cierto tiempo simulando así una velocidad en Hercios.

Por ejemplo, los microprocesadores tienen internamente una señal de reloj, que actualmente suele variar del orden de los 2000-3000 MHzs. En las placas de desarrollo FPGAs podemos tener un reloj de 50-100 MHzs. Así sucesivamente, mediante señales de reloj, podremos disparar acciones y movimientos de los bits de un lado a otro, de un circuito a otro, de un componente a otro. De esta forma es cómo se orquestan realmente las acciones internas de muchos procesamientos digitales..

Continuar leyendo..