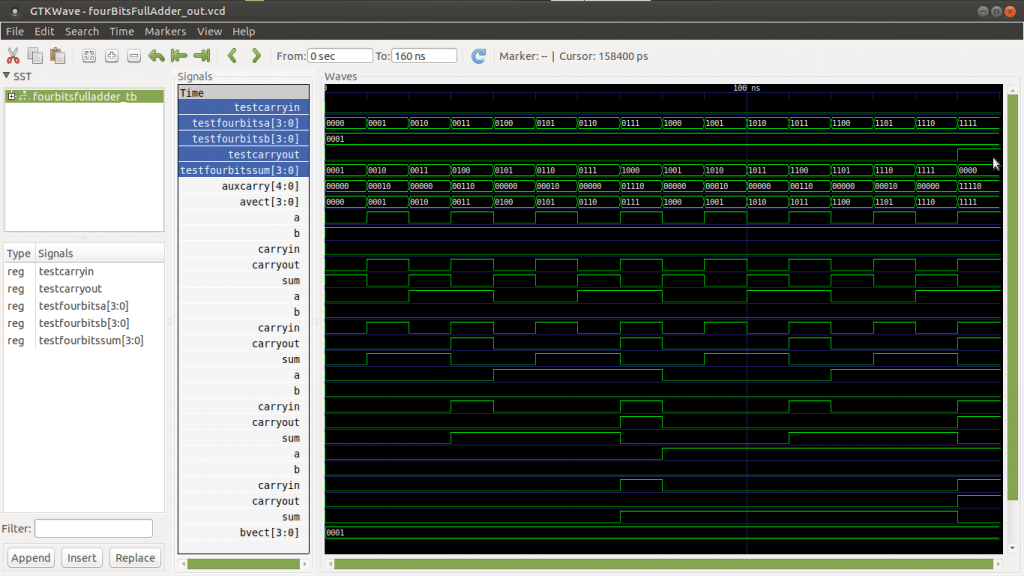

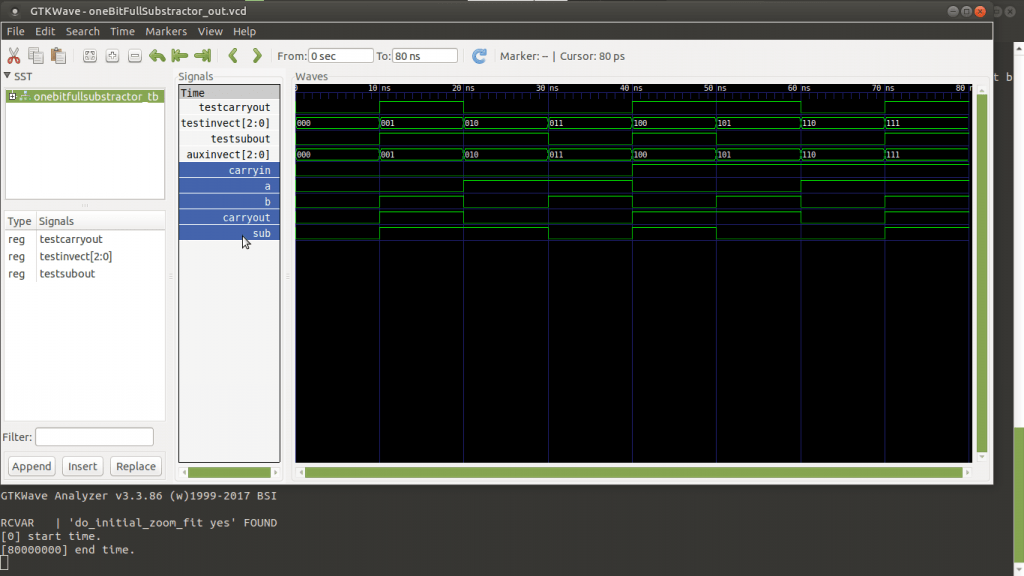

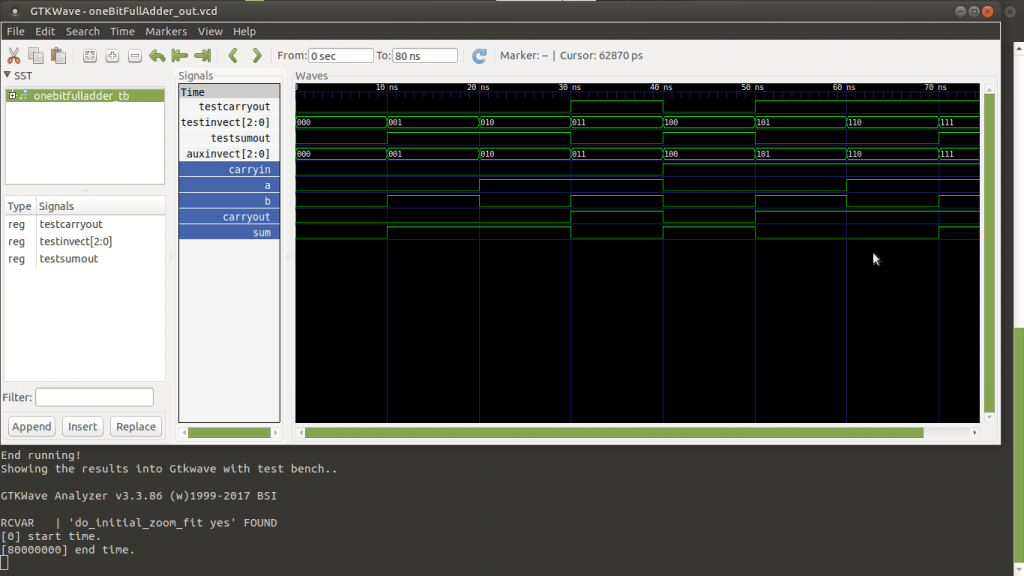

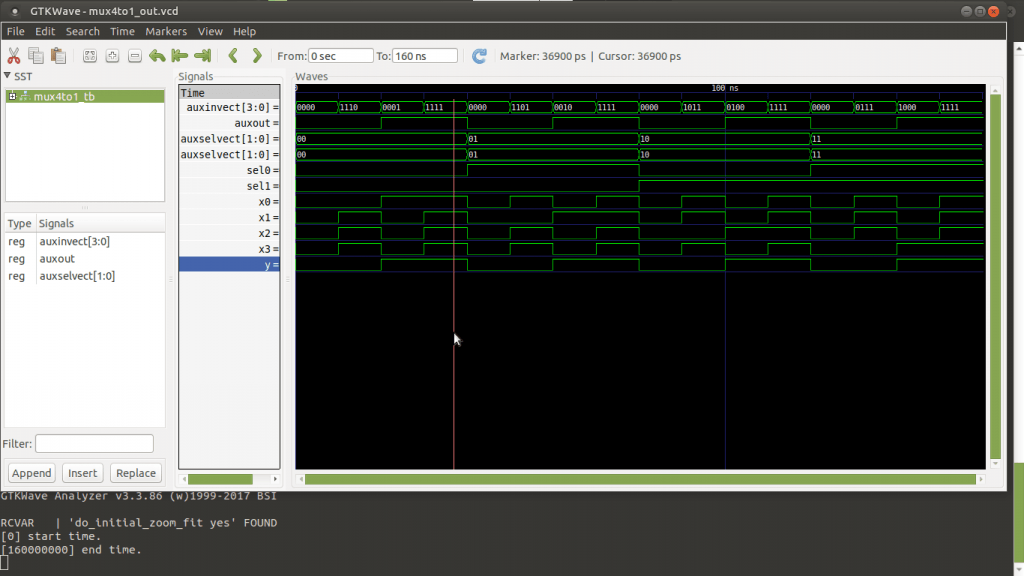

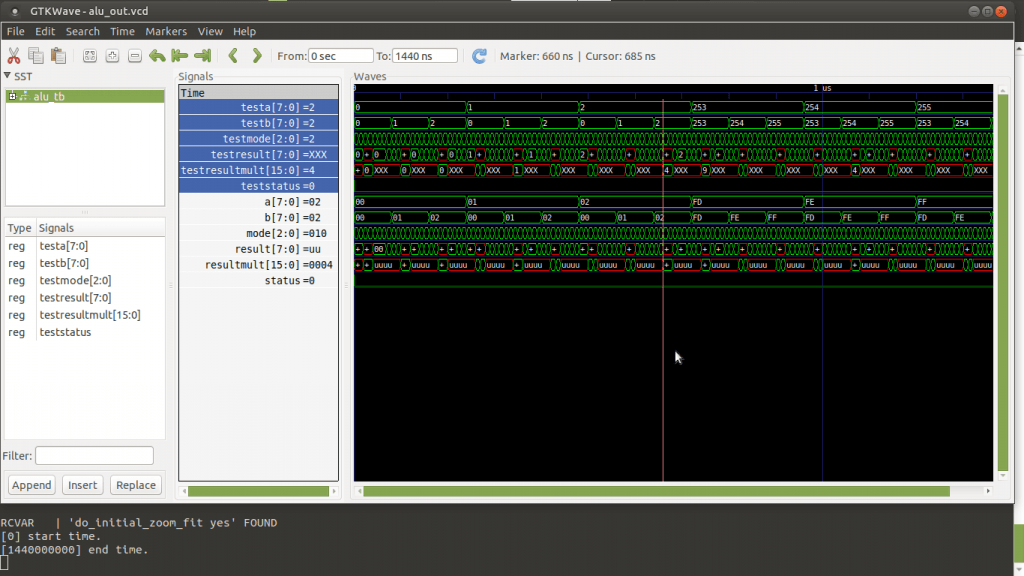

Aquí dejo otro code-kata en VHDL, esta vez de una ALU básica con 8 modos de funcionamiento: suma, resta, multiplicación, exponente a 2, complemento a 2, and, or y not. ALU son las siglas de Arithmetic Logic Unit. Se trata de un componente básico de los procesadores. Resumiendo, es un circuito que recibe unas entradas y saca unas señales de salida, destinado a hacer operaciones aritméticas o lógicas como pueden ser la suma, resta, multiplicación, and, or, etcétera.

En esta ALU tenemos 3 entradas: 2 de ellas son los números, y la tercera entrada es el modo de funcionamiento (la operación que queremos que haga). En las salidas le he puesto 3 salidas: 1 es el resultado básico para la mayoría de estas operaciones, 1 resultado de multiplicación que es un vector de bits más largo, y una salida de estado que aunque no se en éste código usa la idea es dar una señal de éxito 0 o de error 1.

Continuar leyendo..