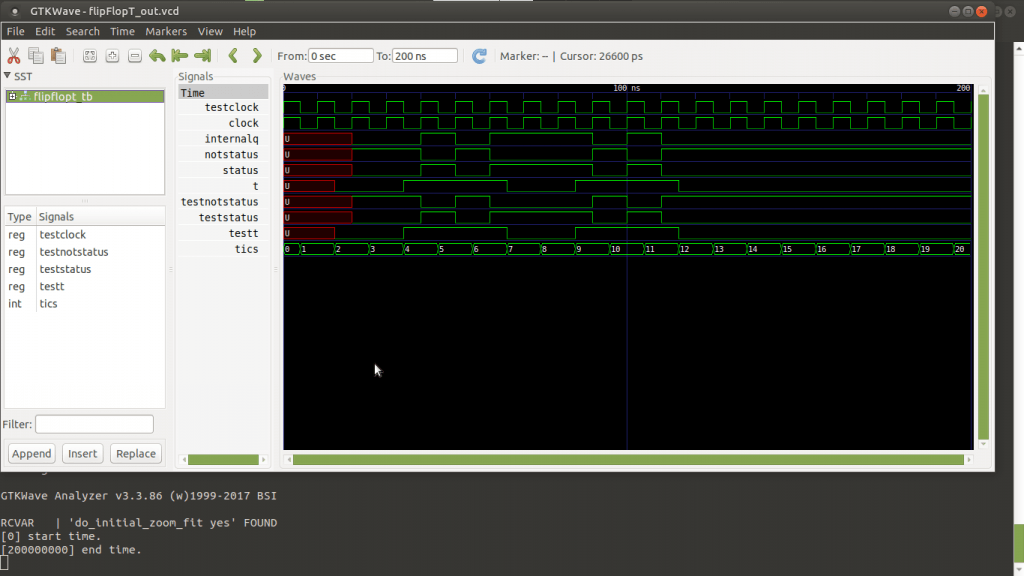

El flip flop T, es el biestable Toggle, que cambia en inglés. Este es un code-kata con el código fuente en VHDL de este biestable. Simplemente es un dispositivo que almacena memoria de un estado.

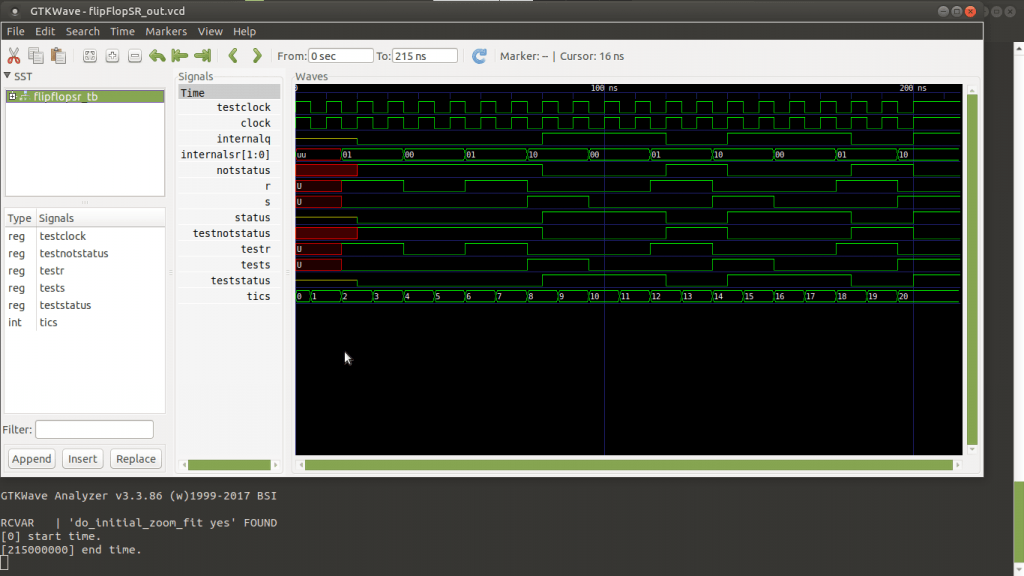

Recibe 2 entradas, una señal de reloj, y la entrada T. Entonces, simplemente si la señal T está activa a 1, entonces con el tic tac del reloj va cambiando las salidas. En las salidas sólo tiene 2 pines, que son el estado actual, y el estado actual negado.

Continuar leyendo..