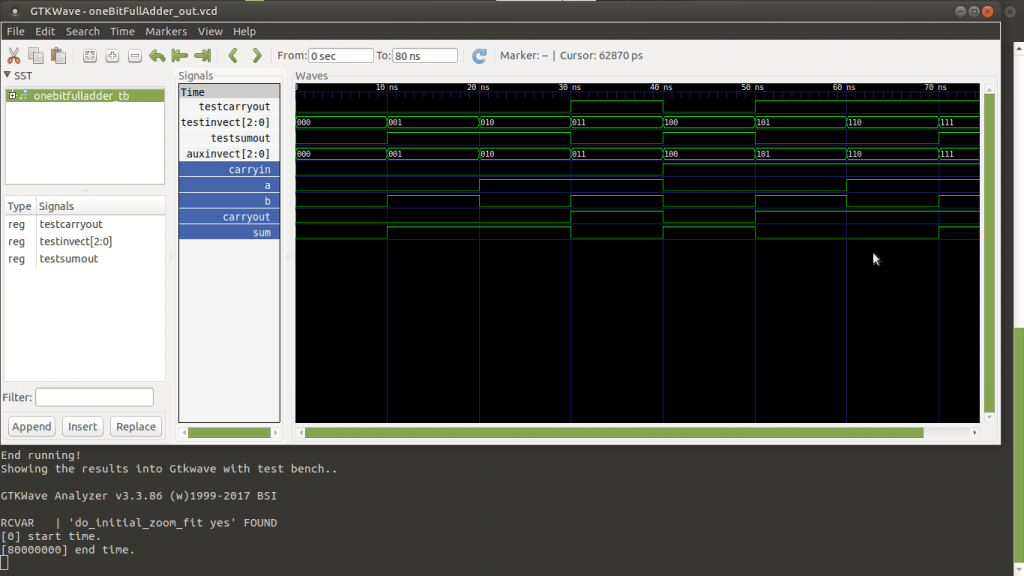

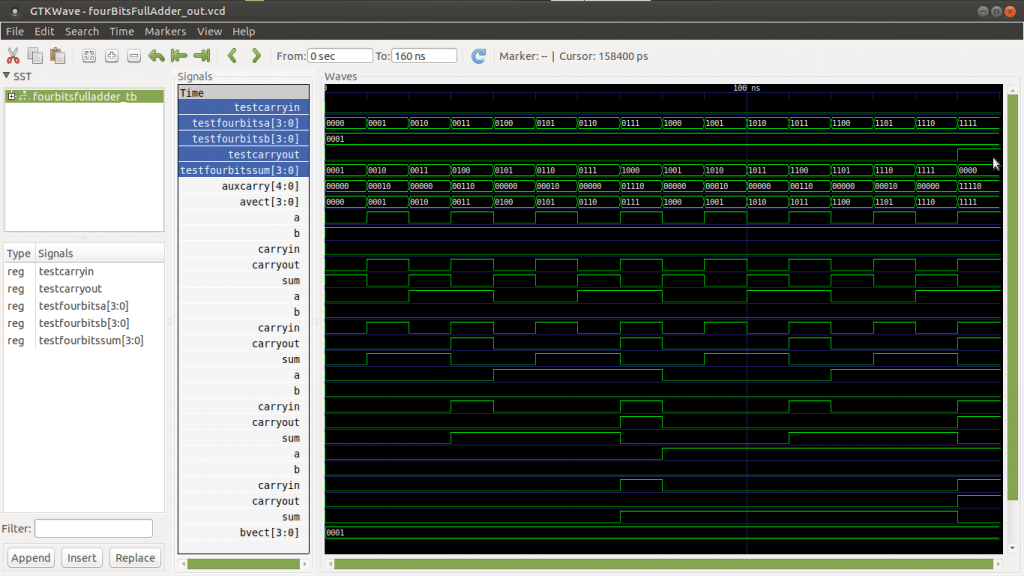

Sigo poniéndome al día en electrónica digital, diseñando circuitos digitales. Así que aquí vuelvo con otro code-kata para hacer un sumador de varios bits. Para este sumador reutilizo un componente previamente hecho, diseñando un sumador completo de 4 bits.

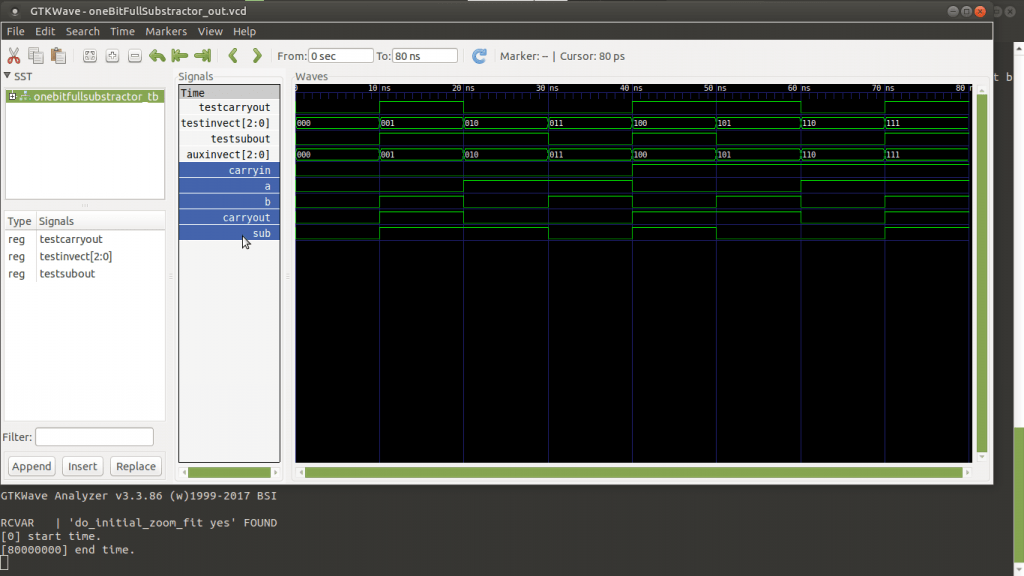

Es decir, en un post anterior escribí un sumador completo simple de 1 bit. Ahora con la instrucción de VHDL llamada port map, podemos enlazar tantos componentes como necesitemos en circuitos más grandes. Usando port map es la forma que tenemos de escalar tanto como queramos, todos los circuitos que queramos en sistemas digitales cada vez más grandes.

Continuar leyendo..