Aquí dejo otro code-kata en VHDL, ahora para construir un restador completo de 1 bit. Recibe 3 entradas y saca 2 salidas. Es muy parecido al sumador completo del post anterior.

La tabla de verdad de este circuito es la siguiente:

| Acarreo de entrada | A | B | Acarreo de salida | Resta |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 0 | 0 |

| 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 |

El código fuente del restador

Las primeras pruebas construyendo sin simplificar, después el simplificado:

-- Sumador completo de 1 bit

library IEEE;

use IEEE.std_logic_1164.all;

entity oneBitFullSubstractor is

port (

sub, carryOut : out std_logic;

a, b, carryIn : in std_logic

);

end entity;

architecture arch of oneBitFullSubstractor is

signal auxInVect : std_logic_vector (2 downto 0);

begin

auxInVect(2) <= carryIn;

auxInVect(1) <= a;

auxInVect(0) <= b;

sub <= '0' when auxInVect = "000" else

'1' when auxInVect = "001" else

'1' when auxInVect = "010" else

'0' when auxInVect = "011" else

'1' when auxInVect = "100" else

'0' when auxInVect = "101" else

'0' when auxInVect = "110" else

'1';

carryOut <= '0' when auxInVect = "000" else

'1' when auxInVect = "001" else

'0' when auxInVect = "010" else

'0' when auxInVect = "011" else

'1' when auxInVect = "100" else

'1' when auxInVect = "101" else

'0' when auxInVect = "110" else

'1';

end architecture;El restador simplificado

De nuevo, utilizando las tablas de Karnaugh llegamos a simplificar el código anterior a este siguiente:

-- Sumador completo de 1 bit

library IEEE;

use IEEE.std_logic_1164.all;

entity oneBitFullSubstractor is

port (

sub, carryOut : out std_logic;

a, b, carryIn : in std_logic

);

end entity;

architecture arch of oneBitFullSubstractor is

begin

sub <= (carryIn and (not a) and (not b))

or ((not carryIn) and (not a) and b)

or (carryIn and a and b)

or ((not carryIn) and a and (not b));

carryOut <= (carryIn and (not a))

or (carryIn and b)

or ((not a) and b);

end architecture;El banco de pruebas

Igual que con el sumador, nos sirve casi el mismo banco de pruebas. Sólo cambio el componente y la nomenclatura de alguna variable:

-- Restador completo de 1 bit

library IEEE;

use IEEE.std_logic_1164.all;

entity oneBitFullSubstractor_tb is

end entity;

architecture arch of oneBitFullSubstractor_tb is

component oneBitFullSubstractor is

port (

sub, carryOut : out std_logic;

a, b, carryIn : in std_logic

);

end component;

signal testInVect : std_logic_vector (2 downto 0);

signal testSubOut, testCarryOut : std_logic;

begin

unit_under_test: oneBitFullSubstractor port map (

sub => testSubOut,

carryOut => testCarryOut,

carryIn => testInVect(2),

a => testInVect(1),

b => testInVect(0)

);

generate_signals : process

begin

testInVect <= "000"; wait for 10 ns;

testInVect <= "001"; wait for 10 ns;

testInVect <= "010"; wait for 10 ns;

testInVect <= "011"; wait for 10 ns;

testInVect <= "100"; wait for 10 ns;

testInVect <= "101"; wait for 10 ns;

testInVect <= "110"; wait for 10 ns;

testInVect <= "111"; wait for 10 ns;

wait;

end process;

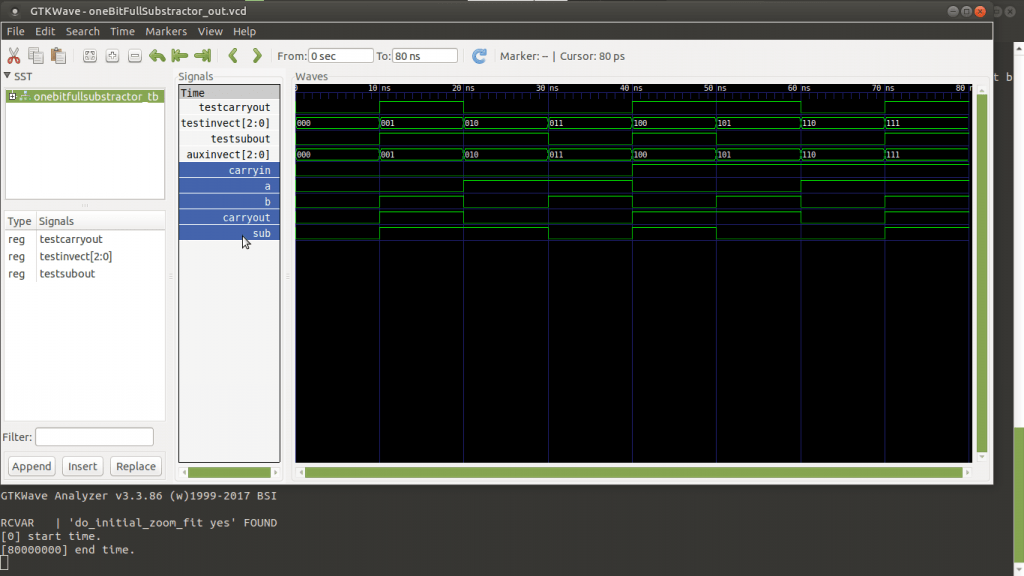

end architecture;Si todo ha ido bien, al visualizar las señales de entrada y salida, tanto con el circuito normal como con el simplificado, se tiene que ver algo como la imagen del principio.