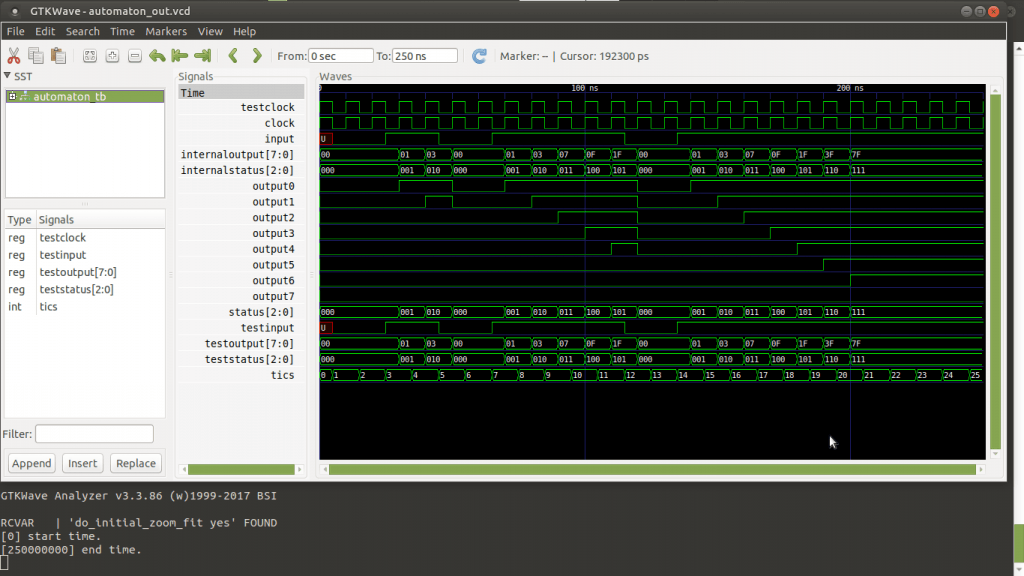

Sigo practicando, poniéndome al día con la creación de circuitos digitales. Si has seguido los últimos posts sobre VHDL, verás que hemos llegado a los autómatas. Estos autómatas, son las partes de los circuitos que controlan los procesos internos de muchos otros componentes. Es decir, las lavadoras, neveras, microondas, televisores, aires acondicionados, alarmas, routers, puentes de comunicación de las placas madre, microprocesadores, etcétera.. llevan autómatas dentro, ya sean máquinas de Moore, de Mealy, finitos, seguros, etc…

Pensemos por ejemplo en un autómata para una aspiradora autónoma, que tenga unos estados de funcionamiento como aspirando, en reposo, en recarga, una serie de sensores de entrada de choque, infrarrojos, ultrasonidos, quizá una cámara, y una serie de actuadores como motores para las ruedas, aspiración.. Pensemos por ejemplo en un autómata para un microondas, en el que vamos seleccionando el programa, le ponemos un tiempo, y le damos al botón de start para que vaya calentando la comida con un contador decreciente de tiempo.. O pensemos por ejemplo en un autómata para controlar unos cultivos hidropónicos, tendrá sensores de agua, temperatura, luces, actuadores para las bombas de agua, quizá ventiladores o ventanas si es un invernadero, altavoces para hacer sonar notificaciones, etc..

Continuar leyendo..