Code-kata para generar un circuito de un multiplexor. En este caso es un multiplexor que recibe 4 señales de entrada y las encauza en una salida eligiendo con otras dos señales de entrada cuál tiene que encauzar a la salida.

Es decir, los 2 pins de entrada para seleccionar nos permiten 4 posibilidades: 00, 01, 10 y 11. Esto nos permite, suponiendo que tenemos 4 señales de entrada x0, x1, x2 y x3; que si seleccionamos 00 en la salida saldrá la señal de entrada x0, si ponemos 01 saldrá la señal x1, si ponemos 10 saldrá la señal x2 y si ponemos en selección 11 saldrá la señal de entrada x3 por la única salida que hay.

¿Sencillo verdad? A ver el código..

El código del multiplexor en VHDL

-- Multiplexor de 4 entradas a 1 con 2 señales de selección.

library IEEE;

use IEEE.std_logic_1164.all;

entity mux4to1 is

port (

y : out std_logic;

sel1, sel0, x3, x2, x1, x0 : in std_logic

);

end entity;

architecture arch of mux4to1 is

-- Señal auxiliar para hacer más legible la selección.

signal auxSelVect : std_logic_vector (1 downto 0);

begin

auxSelVect(1) <= sel1;

auxSelVect(0) <= sel0;

-- La selección de entrada a poner en la salida..

y <= x0 when auxSelVect = "00" else

x1 when auxSelVect = "01" else

x2 when auxSelVect = "10" else

x3 when auxSelVect = "11" else

'U';

end architecture;Ahora el banco de pruebas

-- Multiplexor de 4 entradas a 1 con 2 señales de selección.

library IEEE;

use IEEE.std_logic_1164.all;

-- Una entity vacía.

entity mux4to1_tb is

end entity;

architecture arch of mux4to1_tb is

-- Aquí el componente, el multiplexor en sí.

component mux4to1 port (

y : out std_logic;

sel1, sel0, x3, x2, x1, x0 : in std_logic

);

end component;

-- Señales para conectar con entradas y salidas del componente.

signal auxSelVect : std_logic_vector (1 downto 0);

signal auxInVect : std_logic_vector (3 downto 0);

signal auxOut : std_logic;

begin

-- Conectando todo con el port map.

unit_under_test: component mux4to1 port map (

y => auxOut,

sel1 => auxSelVect(1),

sel0 => auxSelVect(0),

x3 => auxInVect(3),

x2 => auxInVect(2),

x1 => auxInVect(1),

x0 => auxInVect(0)

);

generate_signals: process

begin

-- Tiene que dar 2 a 0 y 2 a 1 en cada grupo de 4:

-- 0011 0011 0011 y 0011 en la salida, para ser correcto.

auxInVect <= "0000"; auxSelVect <= "00"; wait for 10 ns;

auxInVect <= "1110"; auxSelVect <= "00"; wait for 10 ns;

auxInVect <= "0001"; auxSelVect <= "00"; wait for 10 ns;

auxInVect <= "1111"; auxSelVect <= "00"; wait for 10 ns;

auxInVect <= "0000"; auxSelVect <= "01"; wait for 10 ns;

auxInVect <= "1101"; auxSelVect <= "01"; wait for 10 ns;

auxInVect <= "0010"; auxSelVect <= "01"; wait for 10 ns;

auxInVect <= "1111"; auxSelVect <= "01"; wait for 10 ns;

auxInVect <= "0000"; auxSelVect <= "10"; wait for 10 ns;

auxInVect <= "1011"; auxSelVect <= "10"; wait for 10 ns;

auxInVect <= "0100"; auxSelVect <= "10"; wait for 10 ns;

auxInVect <= "1111"; auxSelVect <= "10"; wait for 10 ns;

auxInVect <= "0000"; auxSelVect <= "11"; wait for 10 ns;

auxInVect <= "0111"; auxSelVect <= "11"; wait for 10 ns;

auxInVect <= "1000"; auxSelVect <= "11"; wait for 10 ns;

auxInVect <= "1111"; auxSelVect <= "11"; wait for 10 ns;

wait;

end process;

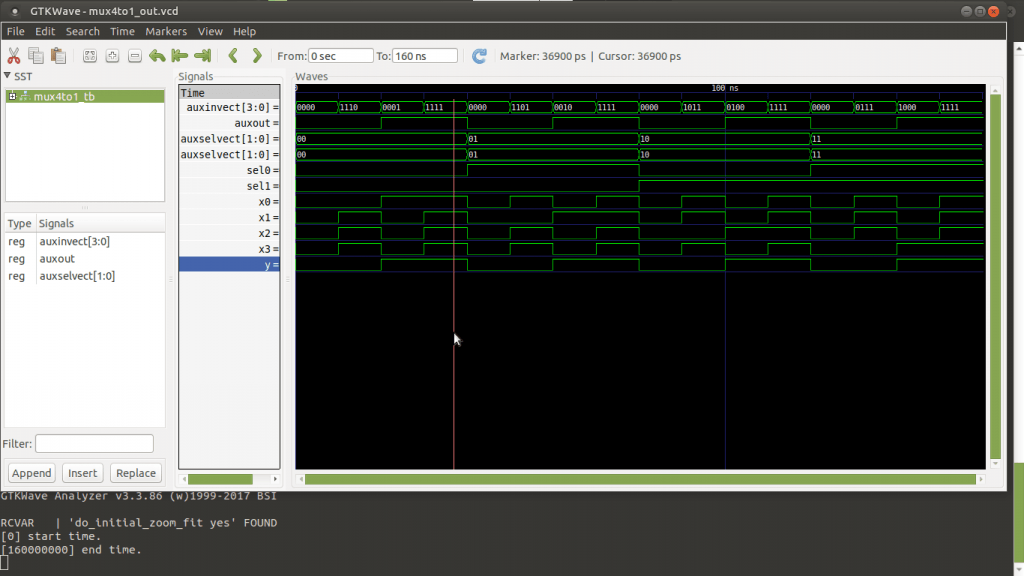

end architecture;De nuevo, otra vez más, si todo ha ido bien tiene que verse una imagen parecida a la de inicio para ver un comportamiento correcto del multiplexor.