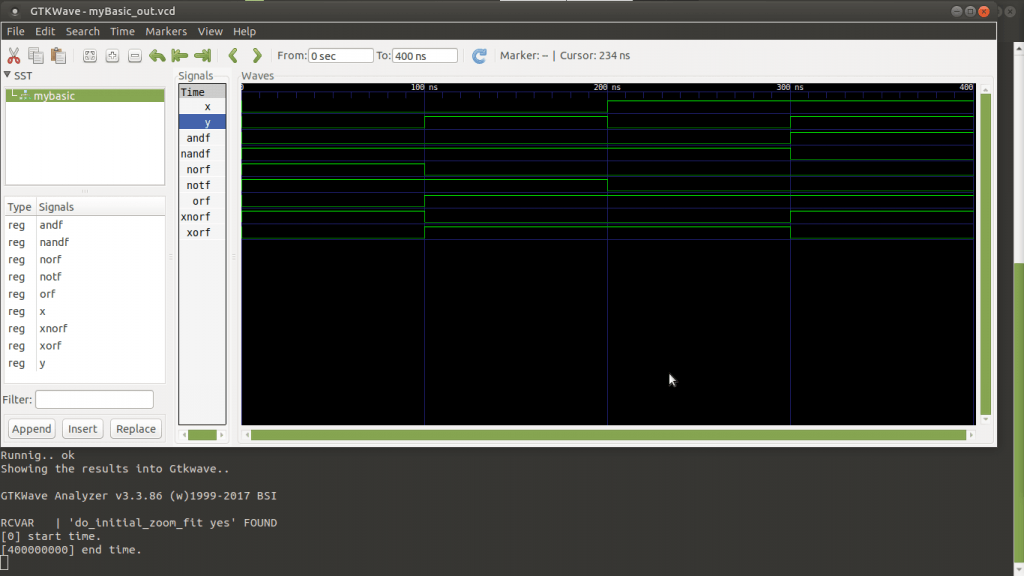

Dejo aquí un code-kata a modo de apunte de consulta. Se trata de un código no sintetizable, ya que no tiene entradas ni salidas, sólo es a modo de pruebas. Una entidad sin entradas ni salidas que asigna concurrentemente señales x y para visualizar en GTKWave los resultados de las puertas lógicas.

Sin muchas explicaciones, es más sencillo leer el código. Tenemos dos partes principales en los ficheros .vhd: la del entity y la del architecture que define el entity.

Es decir, en el entity definimos cómo es este bloque, este circuito. Y en el architecture definimos cómo se comporta, qué señales, cómo combina los impulsos electricos para generar unos resultados.

Al grano, el código

Éste código lo guardo en un fichero llamado myBasic.vhd para probarlo después:

-- Comienzo normal de un fichero vhdl.

-- Librerías.

library IEEE;

use IEEE.std_logic_1164.all;

-- Una entity vacía, no va a ser un circuito sintetizable.

entity myBasic is

end entity;

-- Una arquitectura que simplemente tendrá las señales

-- para ir probando las instrucciones básicas.

architecture arch of myBasic is

-- Son como variables normales y corrientes de otros

-- lenguajes, pero aquí representan señales.

-- Señales de salida:

signal andf, orf, notf, nandf, norf, xorf, xnorf : std_logic;

-- Señales de entrada:

signal x, y : std_logic;

begin

-- El ABC de la lógica binaria ya lo disponible

-- en la librería lógica.

andf <= x and y;

orf <= x or y;

notf <= not x;

nandf <= x nand y;

norf <= x nor y;

xorf <= x xor y;

xnorf <= x xnor y;

-- Un bloque process finalmente para ver los resultados..

procesoDePrueba : process

begin

x <= '0'; y <= '0'; wait for 100 ns;

x <= '0'; y <= '1'; wait for 100 ns;

x <= '1'; y <= '0'; wait for 100 ns;

x <= '1'; y <= '1'; wait for 100 ns;

wait;

end process;

end architecture;Probando un fichero .VHD individual

Normalmente se tienen dos ficheros, uno que define un circuito principal que queremos sintetizar, y otro circuito que realiza las pruebas sobre el principal. El de pruebas simplemente es un circuito que conecta con las entradas y salidas del principal, para entonces inyectarle en las entradas información y así poder chequear si las salidas dan los resultados correctos.

Para ir jugando con los código fuentes en VHDL, he modificado el script del post anterior para así poder probar un fichero que no tiene circuito de pruebas.

#!/bin/bash

# Exit if a command do not returns 0

set -e

if [ "$2" == "--one-file" ]; then

printf "Checking the sintax.. "

ghdl -s $1.vhd

printf "ok\n"

printf "Analyzing.. "

ghdl -a $1.vhd

printf "ok\n"

printf "Elaborating.. "

ghdl -e $1

printf "ok\n"

printf "Runnig.. "

ghdl -r $1 --vcd=$1_out.vcd --stop-time=1000ns

#ghdl -r $1_tb --wave=$1_out.ghw --stop-time=100ns

printf "ok\n"

printf "Showing the results into Gtkwave..\n"

gtkwave $1_out.vcd --rcvar 'do_initial_zoom_fit yes'

#gtkwave $1_out.ghw

else

printf "Checking the sintax.. "

ghdl -s $1.vhd

ghdl -s $1_tb.vhd

printf "ok\n"

printf "Analyzing.. "

ghdl -a $1.vhd

ghdl -a $1_tb.vhd

printf "ok\n"

printf "Elaborating UNIT with test bench.. "

ghdl -e $1_tb

printf "ok\n"

printf "Runnig UNIT with test bench.. "

ghdl -r $1_tb --vcd=$1_out.vcd --stop-time=1000ns

#ghdl -r $1_tb --wave=$1_out.ghw --stop-time=100ns

printf "ok\n"

printf "Showing the results into Gtkwave with test bench..\n"

gtkwave $1_out.vcd --rcvar 'do_initial_zoom_fit yes'

#gtkwave $1_out.ghw

fi

printf "All done!\n"De esta forma, si ahora lanzamos desde línea de comandos el script nuevo, contra el fichero VHDL de pruebas, lo podemos hacer así:

./createAllAndVisualize.sh myBasic --one-fileSi todo ha ido bien, se tiene que ver por pantalla algo como la imagen de arriba.