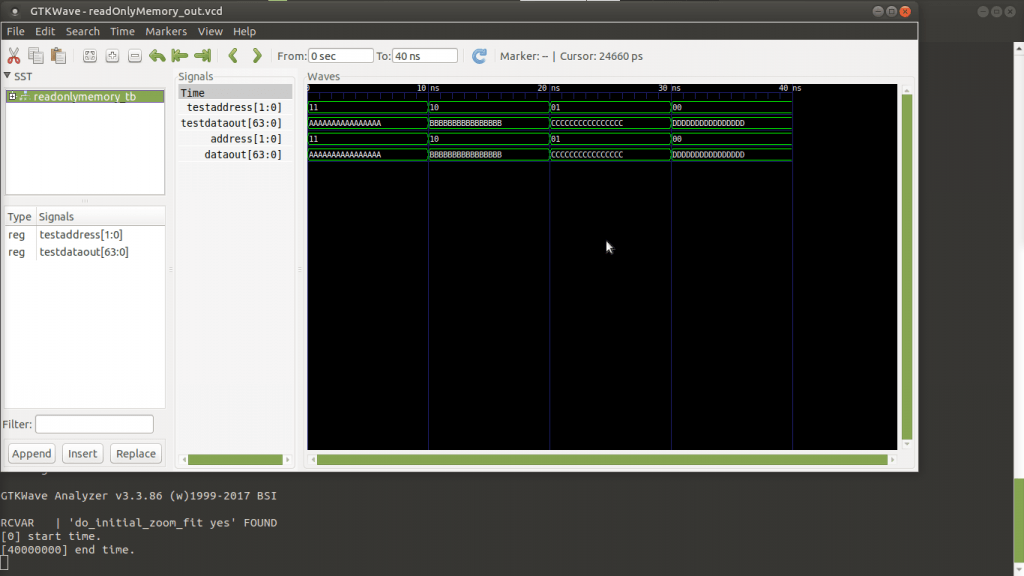

Y aquí otro code-kata, ahora con una memoria de sólo lectura, de las llamadas ROM. Estas memorias simplemente tienen unos datos internamente grabados que pueden ser consultados accediento a direcciones de memoria.

Para este code-kata sólo hay 4 palabras de 64 bits. Es decir un vector de 4 palabras, o una matriz de 4×64 bits, como prefieras verlo. En la entrada recibe 2 pines con las 4 direcciones posibles de palabra.

El código de la ROM

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.numeric_std.all;

entity readOnlyMemory is

port (

dataOut : out std_logic_vector (63 downto 0);

address : in std_logic_vector (1 downto 0)

);

end entity;

architecture arch of readOnlyMemory is

subtype eWord is std_logic_vector (63 downto 0);

type someWords is array (3 downto 0) of eWord;

constant memory : someWords := (

x"AAAAAAAAAAAAAAAA",

x"BBBBBBBBBBBBBBBB",

x"CCCCCCCCCCCCCCCC",

x"DDDDDDDDDDDDDDDD"

);

begin

dataOut <= memory(to_integer(unsigned(address)));

end architecture;El banco de pruebas de la ROM

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.numeric_std.all;

entity readOnlyMemory_tb is

end entity;

architecture arch of readOnlyMemory_tb is

component readOnlyMemory is

port (

dataOut : out std_logic_vector (63 downto 0);

address : in std_logic_vector (1 downto 0)

);

end component;

signal testDataOut : std_logic_vector (63 downto 0);

signal testAddress : std_logic_vector (1 downto 0);

begin

testing_unit: readOnlyMemory port map (

dataOut => testDataOut,

address => testAddress

);

generate_signals : process

begin

for i in 3 downto 0 loop

testAddress <= std_logic_vector(to_unsigned(i,2)); wait for 10 ns;

end loop;

wait;

end process;

end architecture;