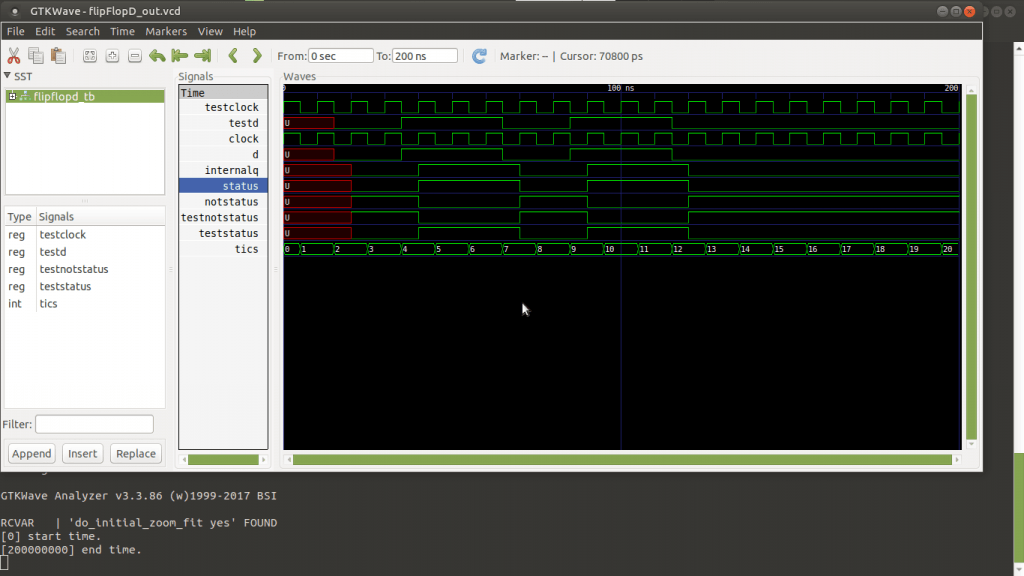

Aquí que dejo otro code-kata sobre electrónica digital, ahora sobre otro tipo de biestable. Este es un circuito que simplemente retarda la señal de salida al son del tic tac del reloj, es el llamado flip flop D, con D de data o de Delay.

Es decir, tenemos 2 señales de entrada, aunque los hay con más señales. En el siguiente código una de las señales es la señal del reloj, y la otra es el dato, un pin de entrada que puede ser 0 o 1. En la salida tendremos dos pines, uno con la salida normal, y otro negada. Simplemente se cambiarán las salidas en el flanco de subida del reloj. Si la entrada de dato es 0, en el siguiente tic tac, se pondrá un 0 en la salida normal, y un 1 en la negada.

Más información en Wikipedia, donde se explica muy bien:

https://es.wikipedia.org/wiki/Biestable#Biestable_D_(Data_o_Delay)

El código fuente del flip flop D

library IEEE;

use IEEE.std_logic_1164.all;

entity flipFlopD is

port (

status, notStatus : out std_logic;

clock, d : in std_logic

);

end entity;

architecture arch_flipFlopD of flipFlopD is

signal internalQ : std_logic;

begin

status <= internalQ;

notStatus <= not internalQ;

main_process : process (clock)

begin

if rising_edge (clock) then

report "Procesando tic tac.. clock=" & std_logic'image(clock);

report " d=" & std_logic'image(d);

internalQ <= d;

end if;

report " internalQ=" & std_logic'image(internalQ);

end process;

end architecture;Un banco de pruebas en VHDL de un flip flop D

library IEEE;

use IEEE.std_logic_1164.all;

entity flipFlopD_tb is

end entity;

architecture arch_flipFlopD_tb of flipFlopD_tb is

component flipFlopD is

port (

status, notStatus : out std_logic;

clock, d : in std_logic

);

end component;

signal testStatus, testNotStatus, testD : std_logic;

signal testClock : std_logic := '0';

signal tics : integer := 0;

begin

testing_unit: flipFlopD port map (

status => testStatus,

notStatus => testNotStatus,

clock => testClock,

d => testD

);

generate_100Mhzs_clock : process

begin

report "Tic tac.. testClock=" & std_logic'image(testClock);

testClock <= not testClock;

if testClock = '1' then tics <= tics + 1; end if;

if tics >= 20 then wait; end if;

wait for 5 ns; -- Tiempo de espera en un flanco de reloj.

end process;

main_process : process

begin

wait for 15 ns;

testD <= '0'; wait for 20 ns;

testD <= '1'; wait for 30 ns;

testD <= '0'; wait for 20 ns;

testD <= '1'; wait for 30 ns;

testD <= '0';

wait;

end process;

end architecture;De nuevo termino diciendo que se debería de ver una gráfica simulada en GTKWave como la de la imagen del principio. Si utilizas otro simulador debería de ser parecido el resultado.