El flip flop T, es el biestable Toggle, que cambia en inglés. Este es un code-kata con el código fuente en VHDL de este biestable. Simplemente es un dispositivo que almacena memoria de un estado.

Recibe 2 entradas, una señal de reloj, y la entrada T. Entonces, simplemente si la señal T está activa a 1, entonces con el tic tac del reloj va cambiando las salidas. En las salidas sólo tiene 2 pines, que son el estado actual, y el estado actual negado.

Este es otro de los biestables de la familia ampliamente utilizados en electrónica para almacenar en memoria cierta información: el flip flop SR, el T, el D o el JK son los más conocidos. Al grano..

El código fuente del flip flop T

library IEEE;

use IEEE.std_logic_1164.all;

entity flipFlopT is

port (

status, notStatus : out std_logic;

clock, t : in std_logic

);

end entity;

architecture arch_flipFlopT of flipFlopT is

signal internalQ : std_logic;

begin

status <= internalQ;

notStatus <= not internalQ;

main_process : process (clock)

begin

if rising_edge (clock) then

report "Procesando tic tac.. clock=" & std_logic'image(clock);

report " t=" & std_logic'image(t);

if internalQ = 'U' then

internalQ <= t;

else

if t = '1' then

internalQ <= not internalQ;

else

internalQ <= internalQ;

end if;

end if;

end if;

report " internalQ=" & std_logic'image(internalQ);

end process;

end architecture;El código fuente del banco de pruebas para el flip flop T

library IEEE;

use IEEE.std_logic_1164.all;

entity flipFlopT_tb is

end entity;

architecture arch_flipFlopT_tb of flipFlopT_tb is

component flipFlopT is

port (

status, notStatus : out std_logic;

clock, t : in std_logic

);

end component;

signal testStatus, testNotStatus, testT : std_logic;

signal testClock : std_logic := '0';

signal tics : integer := 0;

begin

testing_unit: flipFlopT port map (

status => testStatus,

notStatus => testNotStatus,

clock => testClock,

t => testT

);

generate_100Mhzs_clock : process

begin

report "Tic tac.. testClock=" & std_logic'image(testClock);

testClock <= not testClock;

if testClock = '1' then tics <= tics + 1; end if;

if tics >= 20 then wait; end if;

wait for 5 ns; -- Tiempo de espera en un flanco de reloj.

end process;

main_process : process

begin

wait for 15 ns;

testT <= '0'; wait for 20 ns;

testT <= '1'; wait for 30 ns;

testT <= '0'; wait for 20 ns;

testT <= '1'; wait for 30 ns;

testT <= '0';

wait;

end process;

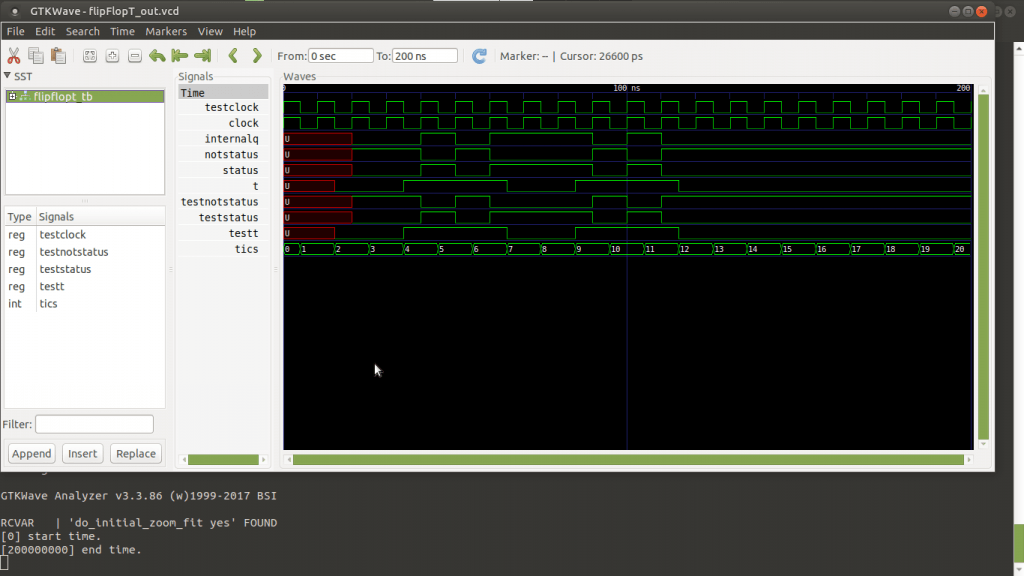

end architecture;Si todo va bien, al simularlo tiene que verse un gráfico como el del principo del post.