Jugando y jugando con VHDL, que llegamos a encontrar una sentencia llamada generate. Con esta generate podemos generar, en pocas líneas, circuitos más grandes que repiten sus componentes. A su vez también tenemos variables, que podemos usar en estos generates.

Con esto junto, reutilizando la ROM anterior, que podemos generar una ROM para nuestras simulaciones de esta forma..

La definición de la ROM con generates y variables generic

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.numeric_std.all;

entity readOnlyMemory is

-- Variables para generar el circuito

-- de tamaño variable según definición.

generic (

WORDSIZE : integer;

BITSADDRESS : integer;

QTYADDRESSES : integer

);

port (

dataOut : out std_logic_vector (WORDSIZE-1 downto 0);

address : in std_logic_vector (BITSADDRESS-1 downto 0)

);

end entity;

architecture arch of readOnlyMemory is

subtype eWord is std_logic_vector (WORDSIZE-1 downto 0);

type someWords is array (QTYADDRESSES-1 downto 0) of eWord;

signal memory : someWords;

begin

-- Genera las palabras de valor igual a un número..

generate_values : for i in QTYADDRESSES-1 downto 0 generate

-- Convierte el entero del bucle en representación binaria

-- del entero en tamaño WORDSIZE, y a su vez estos bits a vector de bits.

memory(i) <= std_logic_vector(to_unsigned(i,WORDSIZE));

end generate;

-- Se direcciona con un parámetro entero..

dataOut <= memory(to_integer(unsigned(address)));

end architecture;El banco de pruebas para visualizar si funciona bien

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.numeric_std.all;

entity readOnlyMemory_tb is

-- Definimos unas variables globales al test

-- para definir la memoria ROM y

-- su recorrido posterior..

generic (

TESTWORDSIZE : integer := 64;

TESTBITSADDRESS : integer := 4;

TESTQTYADDRESSES : integer := 16

);

end entity;

architecture arch of readOnlyMemory_tb is

-- Reutilizamos la ROM..

component readOnlyMemory is

generic (

WORDSIZE : integer := TESTWORDSIZE;

BITSADDRESS : integer := TESTBITSADDRESS;

QTYADDRESSES : integer := TESTQTYADDRESSES

);

port (

dataOut : out std_logic_vector (WORDSIZE-1 downto 0);

address : in std_logic_vector (BITSADDRESS-1 downto 0)

);

end component;

signal testDataOut : std_logic_vector (TESTWORDSIZE-1 downto 0);

signal testAddress : std_logic_vector (TESTBITSADDRESS-1 downto 0);

begin

-- Conectamos la ROM al banco de pruebas..

testing_unit: readOnlyMemory port map (

dataOut => testDataOut,

address => testAddress

);

generate_signals : process

begin

-- Le ponemos en los pines de dirección las señales

-- para ver que sale en testDataOut..

for i in TESTQTYADDRESSES-1 downto 0 loop

testAddress <= std_logic_vector(to_unsigned(i,TESTBITSADDRESS)); wait for 10 ns;

end loop;

wait;

end process;

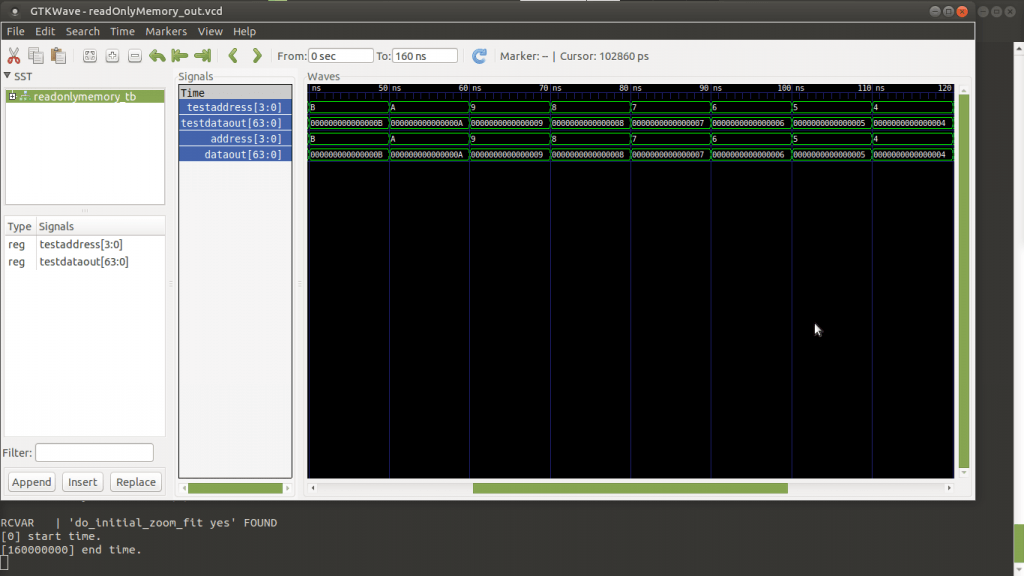

end architecture;De nuevo, si todo ha ido bien, se tiene que ver una imagen como la del principio.