Aquí vengo de nuevo con más code-katas, ahora con un flip flop SR. Un flip flop es un biestable, un circuito multivibrador que permanece en dos estados, mientras las señales de entrada no cambian. Se suelen usar mucho en electrónica para almacenar bits.

El flip flop SR es un biestable que con sus dos entradas se pone a 0 o a 1. Con la entrada R se pone a cero, y con la S a 1. Simple y llanamente este es el funcionamiento. Si recibe tanto R como S a cero, entonces permanece en el estado que tenga. Y si recibe R y S a 1, está prohibido, con lo que entra en un estado inestable.

Más información sobre los biestables aquí:

https://es.wikipedia.org/wiki/Biestable

El código fuente del flip flop SR

library IEEE;

use IEEE.std_logic_1164.all;

entity flipFlopSR is

port (

status, notStatus : out std_logic;

clock, s, r : in std_logic

);

end entity;

architecture arch_flipFlopSR of flipFlopSR is

signal internalQ : std_logic;

signal internalSR : std_logic_vector (1 downto 0);

begin

status <= internalQ;

notStatus <= not internalQ;

main_process : process (clock)

begin

internalSR <= s & r;

if rising_edge (clock) then

report "Procesando tic tac.. clock=" & std_logic'image(clock);

report " s=" & std_logic'image(s);

report " r=" & std_logic'image(r);

if internalSR = "00" then

--internalQ <= internalQ;

elsif internalSR = "01" then

internalQ <= '0';

elsif internalSR = "10" then

internalQ <= '1';

else -- internalSR is "11"

-- Esto no está permitido, queda en estado inestable.

internalQ <= 'Z';

end if;

end if;

end process;

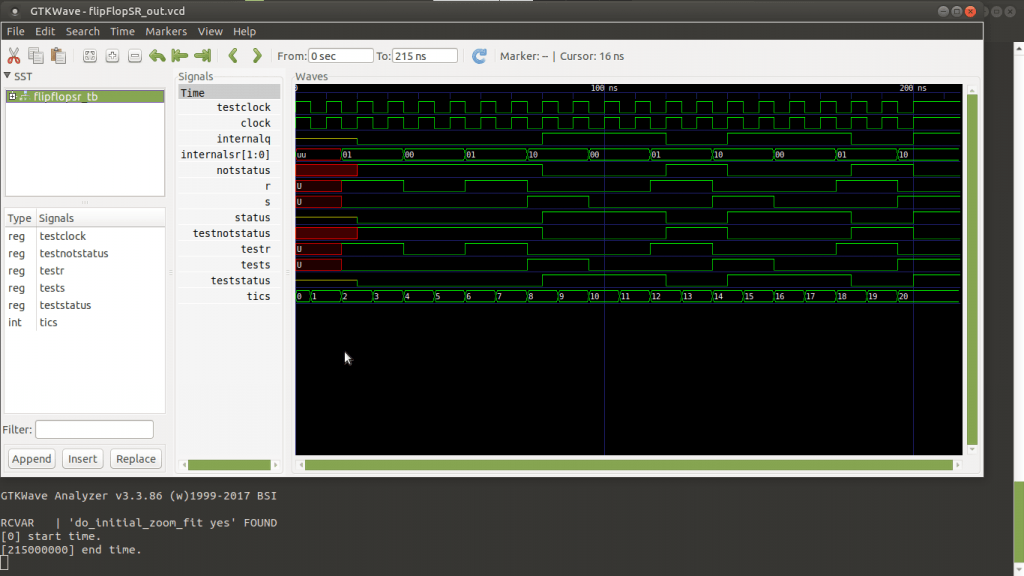

end architecture;El código fuente del banco de pruebas del flip flop SR

library IEEE;

use IEEE.std_logic_1164.all;

entity flipFlopSR_tb is

end entity;

architecture arch_flipFlopSR_tb of flipFlopSR_tb is

component flipFlopSR is

port (

status, notStatus : out std_logic;

clock, s, r : in std_logic

);

end component;

signal testStatus, testNotStatus, testS, testR : std_logic;

signal testClock : std_logic := '0';

signal tics : integer := 0;

begin

testing_unit: flipFlopSR port map (

status => testStatus,

notStatus => testNotStatus,

clock => testClock,

s => testS,

r => testR

);

generate_100Mhzs_clock : process

begin

report "Tic tac.. testClock=" & std_logic'image(testClock);

testClock <= not testClock;

if testClock = '1' then tics <= tics + 1; end if;

if tics >= 20 then wait; end if;

wait for 5 ns; -- Tiempo de espera en un flanco de reloj.

end process;

main_process : process

begin

wait for 15 ns;

-- Reset inicial

testS <= '0'; testR <= '1'; wait for 20 ns;

testS <= '0'; testR <= '0'; wait for 20 ns;

testS <= '0'; testR <= '1'; wait for 20 ns;

testS <= '1'; testR <= '0'; wait for 20 ns;

--testS <= '1'; testR <= '1'; wait for 20 ns;

testS <= '0'; testR <= '0'; wait for 20 ns;

testS <= '0'; testR <= '1'; wait for 20 ns;

testS <= '1'; testR <= '0'; wait for 20 ns;

--testS <= '1'; testR <= '1'; wait for 20 ns;

testS <= '0'; testR <= '0'; wait for 20 ns;

testS <= '0'; testR <= '1'; wait for 20 ns;

testS <= '1'; testR <= '0'; wait for 20 ns;

--testS <= '1'; testR <= '1'; wait for 20 ns;

wait;

end process;

end architecture;